H.264/AVC视频编码变换量化核的硬件设计

2012/01/17

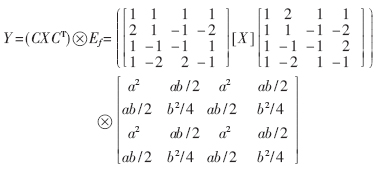

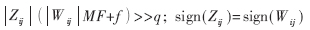

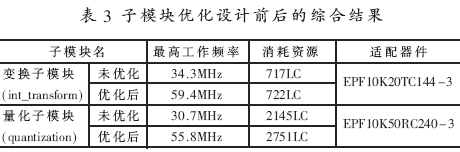

摘要:基于H.264/AVC视频编码标准,完成了编码模块中的4×4整数变换量化核的分析和硬件实现的优化设计。通过三种优化设计处理后,在硬件开销改变不大的情况下,使4×4整数变换量化核的最高工作频率相比优化前的30.7MHz提高了82%,达到55.8MHz,为H.264/AVC视频编码标准的硬件实现提供了参考。

《电子技术应用》

| “全球眼”行业应用丰富 视频监控朝高清时代迈进 2012-01-12 |

| 基于DM642的视频音频监控系统设计 2012-01-10 |

| 基于GPRS的大屏幕LED显示系统的设计和实现 2012-01-10 |

| 高清监控行业走向纵深 系统建设“端到端”是关键 2011-12-20 |

| 多媒体融合调度 沟通变革正当时 2011-11-22 |